加法和减法

减法: 将负数用二进制补码的形式表现出来并相加

补码: 除了符号位,其他位置 取反 + 1

正数 👉 负数补码: 全部取反 +1

负数补码 👉 正数 : 全部取反 +1

减法就是: 将 相同符号 的 数相减 变成 相反符号 的数相加

溢出意味着:符号位被结果值占去

加法运算溢出

原因:符号位被进位填充

当两个正数相加:符号位为1表示溢出,为0就没事

两个负数相加:符号位为0表示溢出

减法运算溢出

正数 - 负数 = 负数

负数 - 正数 = 正数

原因:符号位借位现象

小结

无论数的表示形式如何,只要你用有限字长表示(64位,32位...),就一定会有溢出

即使无符号数溢出好检测,经常用自然数做地址运算,程序一般不许需要检测地址计算的事,所以容易被忽略

有符号数的运算采用补码形式,溢出检测情况更复杂,但是必须要有

饱和操作,意思就是当计算溢出时,用最大正数/最小负数来表示。比如手机音量最大也就是满条

乘法

乘法就是单个单个数去× 被乘数 ,然后结果相加

m位A n位B 相乘结果有 m+n 位,所以有溢出可能

用0,1进制乘法,有1就照搬,有0就全0

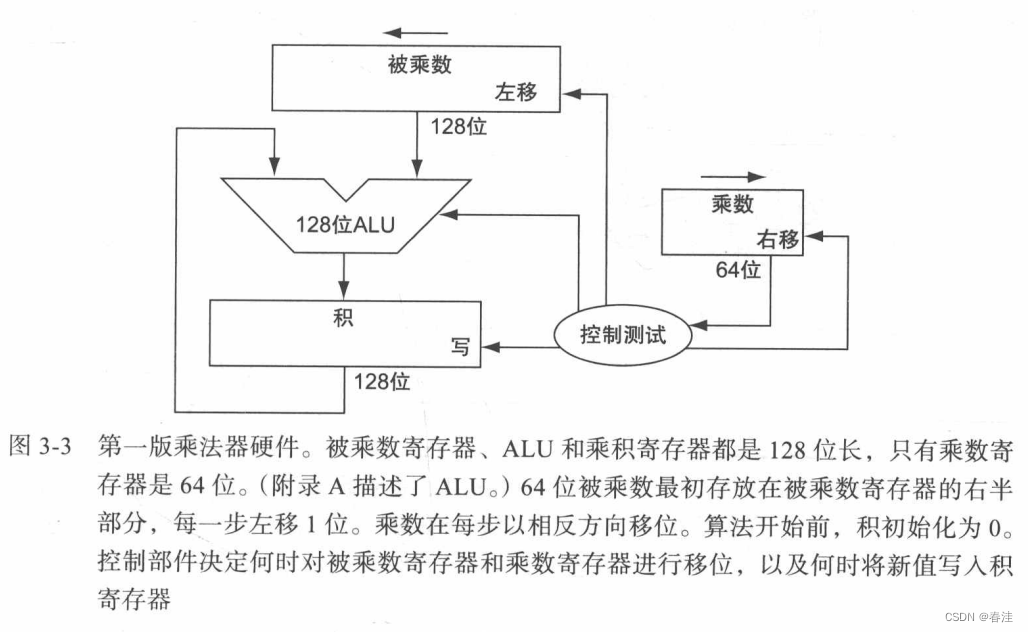

串行乘法

开局初始化:积寄存器为0;被乘数寄存器因为要移位,所以左64为0,右64为被乘数

乘数每次计算只提供1个数,所以不用128

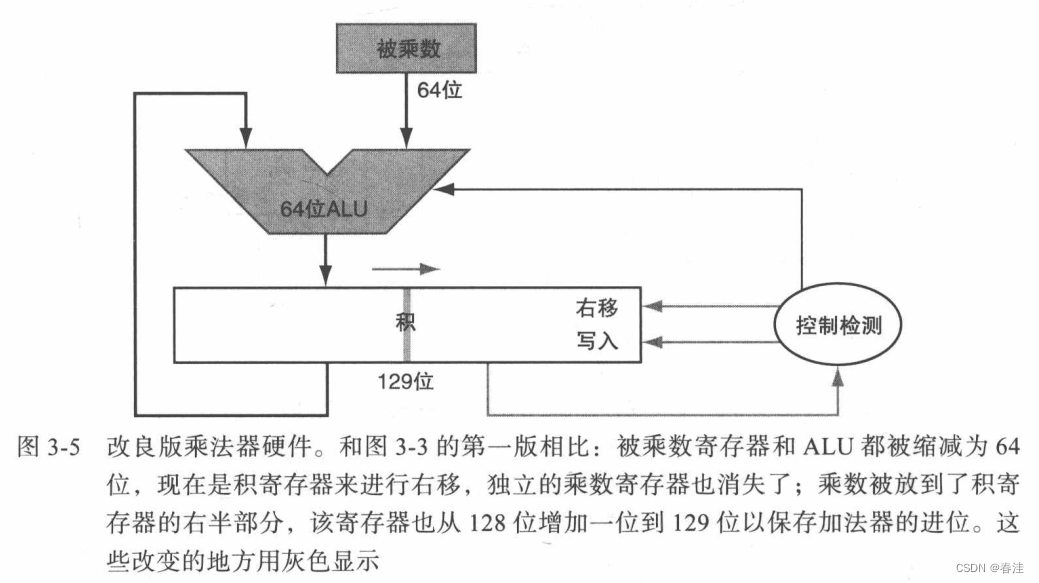

改进乘法器

因为在老结构中:积的寄存器有严重空缺,所以得想办法填补,正好,因为被乘数,乘数都需要右移;

积和乘数开始都在积寄存器里,但是积寄存器不断右移,右半段是乘数,让它不断右移,弹出最低位,拿去判断是否压入被乘数,这样可以填充寄存器

总结:上边我们采用进位检测 + 加法的操作实现了乘法运算

又改良了寄存空挡的缺点,采用积 & 乘数 联动的方式进行运算,减少了寄存器数量

但是我们这里是正数乘法,如何处理带符号乘法?

带符号乘法

最基本的想法:检测异号,记住结果符号,然后采用无符号乘法

对于我们之前学的移位寄存乘法,如果出现带符号数的话,会导致移位之前的符号位变成了移位之后的值,我们采用符号位填充的方式来代替原操作数进行乘法,左半段的结果右移的时候将最高位留一下作为符号扩展,算到最后取右64位就ok了

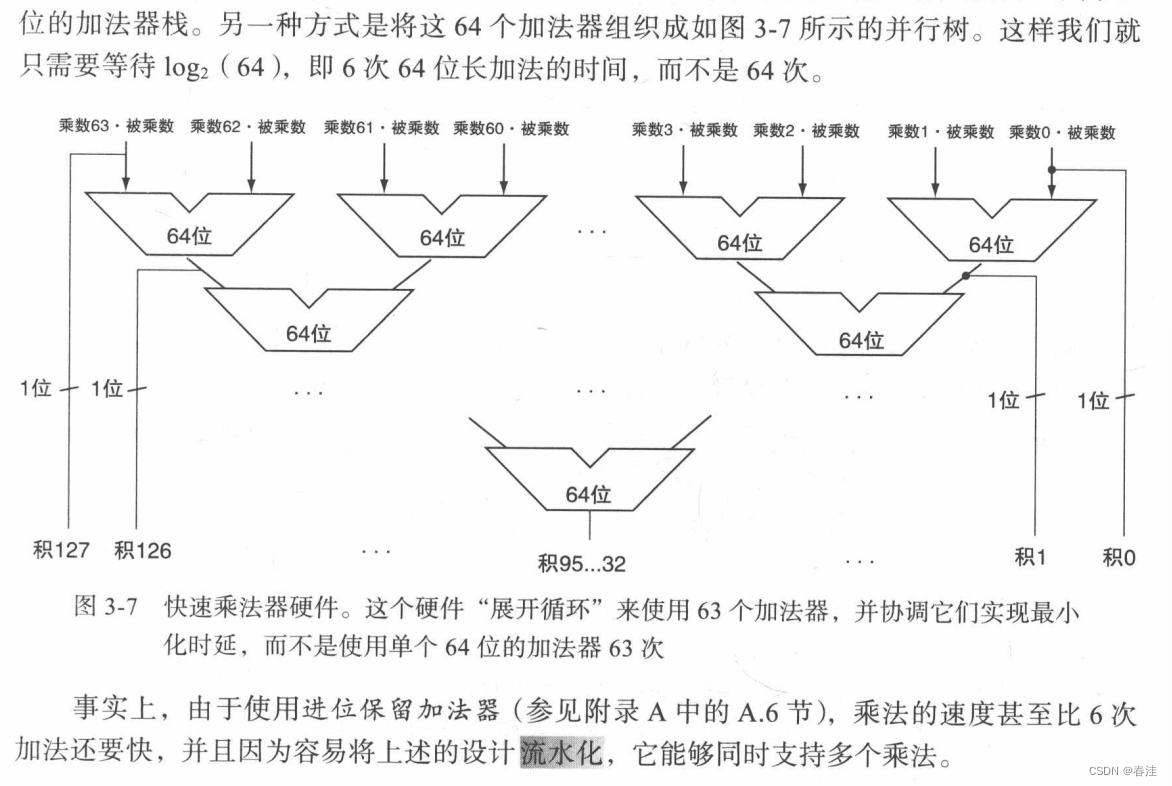

带符号快速乘法

法1: 弄64个加法器,然后排成一个 斜/ 形状,每个位都和被乘数与一遍,然后直接相加,理论上来说只需要64个周期就可以完成了

法2:

RISC-V中的乘法

mul

mulh

mulhsu

mulhu

总结

总的来说,乘法就是移位和相加

如果是2的幂级数乘法,直接移位即可

我们乘法的地方不可避免,但是加法的地方我们可以尽量改善

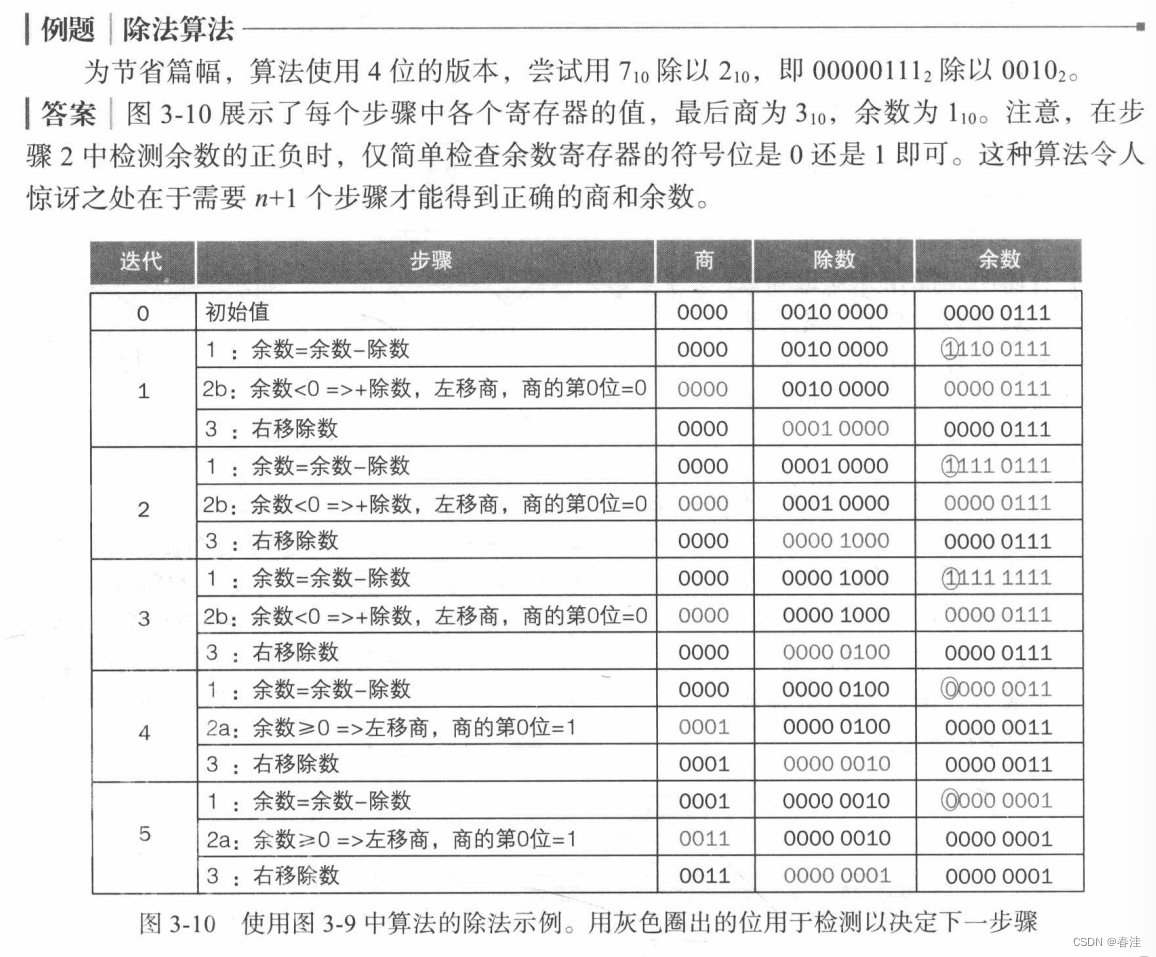

除法运算

除法算法和硬件实现

开始时:64位商寄存器置0,余数寄存器放被除数。

我们除法开始从高位去比数的时候其实就是忽略了低位的那些0(因为写起来省事)

所以,开始时,除数寄存器128位,从左半段开始右移,其实就是慢慢的往下比数的过程,把低位的0慢慢吞掉,并和被除数比较大小。大则0;小则减,然后1。商是从右往左,最终形成结果

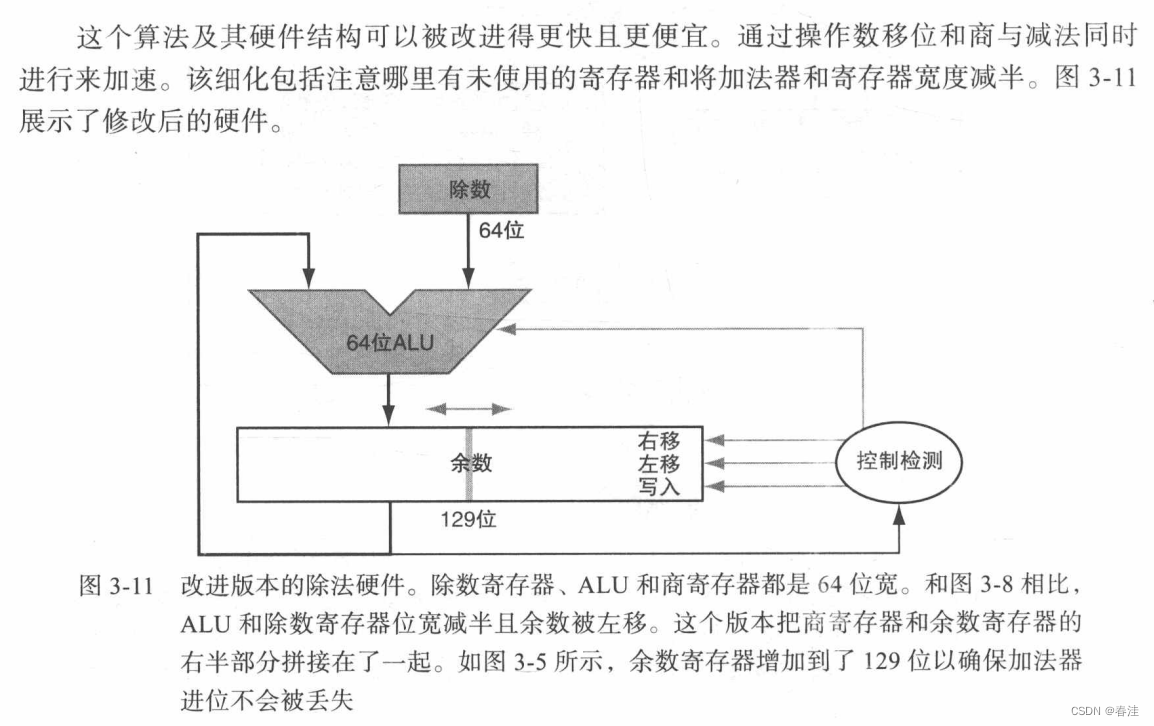

改进除法器

我们除法本来靠的是除数吃0右移,现在改良节省内存其实就是让被除数左移,带动商左移,所以让商和余数寄存器拼接在一起;

有符号除法

记住符号,然后转化为无符号除法

有符号除法原则:

异号:商为负值,余数和被除数同号

同号:商为正值,余数和被除数同号

快速除法

SRT除法